DrBackhands

Student

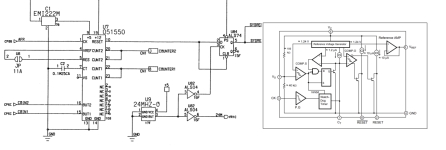

I probed IC 051550 and found my Simpsons board is watchdogging

RES and RESET just pulse, but when I bridge the JP connecting RES (p5) and VREF (p4), RES is stuck low but RESET (p10) is stuck high.

RES and RESET just pulse, but when I bridge the JP connecting RES (p5) and VREF (p4), RES is stuck low but RESET (p10) is stuck high.

Additional info: Voltage at VS is 1.4V and the voltage at CT is 1.224V, which as I understand it from the datasheet, should be high enough to not trigger the watchdog circuit. CK is stuck high. I'm getting a healthy 5V and 12V to the IC at pins 9 and 19.

My question: If the JP is bridged and RES (p5) is stuck low, should RESET still be stuck high? Is the IC doing what it's suppose to be doing? And just to confirm, if RESET is stuck high all the way to the CPU, that means the board won't boot, right? I'm not getting low and high confused here, right?

Edit (10/21): I was getting high and low confused. The CPU is getting a high signal on the RES pin which is what should be happening.

Additional info: Voltage at VS is 1.4V and the voltage at CT is 1.224V, which as I understand it from the datasheet, should be high enough to not trigger the watchdog circuit. CK is stuck high. I'm getting a healthy 5V and 12V to the IC at pins 9 and 19.

My question: If the JP is bridged and RES (p5) is stuck low, should RESET still be stuck high? Is the IC doing what it's suppose to be doing? And just to confirm, if RESET is stuck high all the way to the CPU, that means the board won't boot, right? I'm not getting low and high confused here, right?

Edit (10/21): I was getting high and low confused. The CPU is getting a high signal on the RES pin which is what should be happening.

Attachments

Last edited: